AMD pr├żsentiert ARM-Opteron Seattle auf der Hot Chips 26

Auf der der┬Łzeit statt┬Łfin┬Łden┬Łden Pro┬Łzes┬Łsor┬Łkon┬Łfe┬Łrenz Hot Chips pr├ż┬Łsen┬Łtier┬Łte AMD Details zu ihrem ers┬Łten ARM-SoC, der Ende des Jah┬Łres auf dem Markt erwar┬Łtet wird.

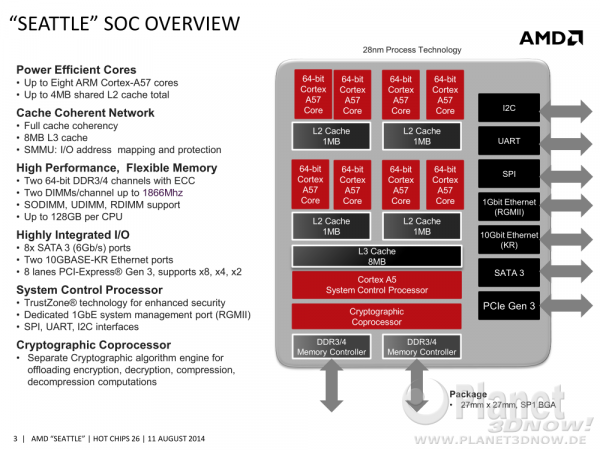

Wie bereits l├żn┬Łger bekannt, basiert der Chip auf vor┬Łge┬Łfer┬Łtig┬Łten Kom┬Łpo┬Łnen┬Łten von ARM, ins┬Łbe┬Łson┬Łde┬Łre auf ARMs Cor┬Łtex-A57-Ker┬Łnen, von denen maxi┬Łmal acht ver┬Łbaut wer┬Łden. Wie es sich f├╝r einen voll┬Łwer┬Łti┬Łges Sys┬Łtem geh├Črt, befin┬Łden sich au├¤er┬Łdem wei┬Łte┬Łre I/OŌĆæKomponenten auf dem Chip: zwei Spei┬Łcher┬Łka┬Łn├ż┬Łle (wahl┬Łwei┬Łse im DDR3- oder DDR4-Betrieb), zwei 10-Gbit-Ether┬Łnet-Anschl├╝s┬Łse, ein Gbit-Anschluss f├╝r eine siche┬Łre Ver┬Łbin┬Łdung zum Trust┬Łzo┬Łne-ARM5-Kern sowie acht PCIeŌĆæ3.0ŌĆæLeitungen und acht SATA3-Anschl├╝sse.

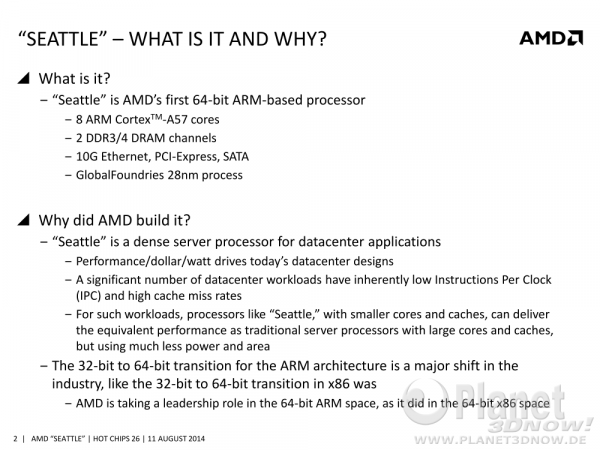

Au├¤er┬Łdem ver┬Łweist AMD noch┬Łmals auf die Gr├╝n┬Łde f├╝r den Schwenk hin zur ARM-Archi┬Łtek┬Łtur. Dem┬Łnach ver┬Łur┬Łsach┬Łten vie┬Łle Ser┬Łve┬Łr┬Łap┬Łpli┬Łka┬Łtio┬Łnen nur eine gerin┬Łge Pro┬Łzes┬Łsor┬Łlast, wel┬Łche somit von rela┬Łtiv schwa┬Łchen ARM-Ker┬Łnen pro┬Łblem┬Łlos erle┬Łdigt wer┬Łden kann. Im Gegen┬Łzug erh├żlt man daf├╝r eine h├Čhe┬Łre Ener┬Łgie┬Łef┬Łfi┬Łzi┬Łenz, die umso st├żr┬Łker ins Gewicht f├żllt, je mehr CPUs ver┬Łwen┬Łdet wer┬Łden. Da Ser┬Łver┬Łfar┬Łmen bekannt┬Łlich aus tau┬Łsen┬Łden Sys┬Łte┬Łmen und noch mehr CPUs bestehen, ist AMDs Ansatz nachvollziehbar.

Es wird erwar┬Łtet, dass AMD auch sei┬Łne eige┬Łne Ver┬Łbin┬Łdungs┬Łtech┬Łno┬Łlo┬Łgie ŌĆ£Free┬Łdom FabricŌĆØ inte┬Łgriert, die durch Zusatz┬Łchips auf den von Sea┬Łmi┬Łcro ├╝ber┬Łnom┬Łme┬Łnen Ser┬Łvern bereits Ver┬Łwen┬Łdung fin┬Łden. Dadurch k├Čnn┬Łte die Ener┬Łgie┬Łef┬Łfi┬Łzi┬Łenz durch das gemein┬Łsa┬Łme N├╝t┬Łzen von I/OŌĆæAnbindungen wei┬Łter gestei┬Łgert wer┬Łden. Jedoch gibt es zu die┬Łsem Zeit┬Łpunkt dazu kei┬Łne offi┬Łzi┬Łel┬Łlen Verlautbarungen.

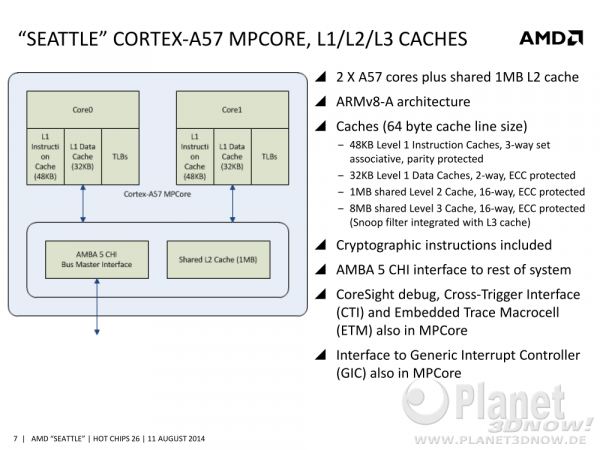

Als Caches ste┬Łhen jedem Cor┬Łtex-A57-Kern 48 kB L1-Instruk┬Łti┬Łons- und 32 kB-L1-Daten┬Łcache zur Ver┬Łf├╝┬Łgung. Zwei Ker┬Łne tei┬Łlen sich auf der n├żchs┬Łten Stu┬Łfe dann ein Mega┬Łbyte L2-Cache (also 4 MB L2-Cache ins┬Łge┬Łsamt f├╝r 8 Ker┬Łne), der L3-Cache ist 8 MB gro├¤. Wie es sich f├╝r einen Ser┬Łver┬Łpro┬Łzes┬Łsor geh├Črt, sind alle Daten┬Łcaches durch ECC abgesichert.

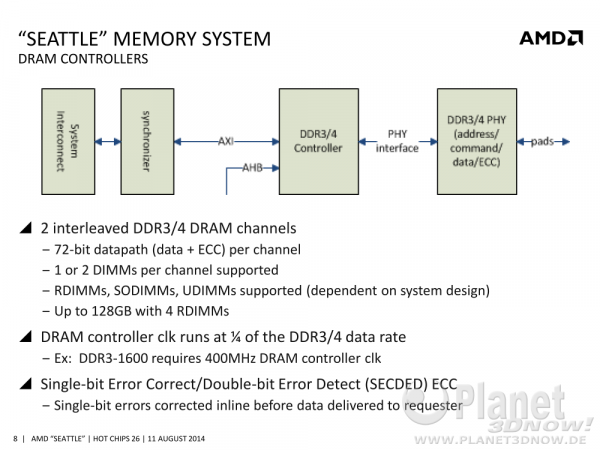

Bereits erw├żhnt wur┬Łde die Unter┬Łst├╝t┬Łzung von DDR3- oder DDR4-Spei┬Łcher┬Łmo┬Łdu┬Łlen, letz┬Łte┬Łre tauch┬Łten gera┬Łde auf dem deut┬Łschen Markt auf. Wie schon bei den Caches ver┬Łsteht sich die Unter┬Łst├╝t┬Łzung von ECC, sodass pro Kanal 72 Bit pro Takt ├╝ber┬Łtra┬Łgen wer┬Łden. Als maxi┬Łma┬Łle Spei┬Łcher┬Łgr├Č┬Ł├¤e gibt AMD 128 Giga┬Łbyte bei Ein┬Łsatz von regis┬Łtered Modu┬Łlen an. Der DRAM-Con┬Łtrol┬Łler wird mit einem Vier┬Łtel des Spei┬Łcher┬Łtak┬Łtes betrie┬Łben, d.h. um 400 Mhz.

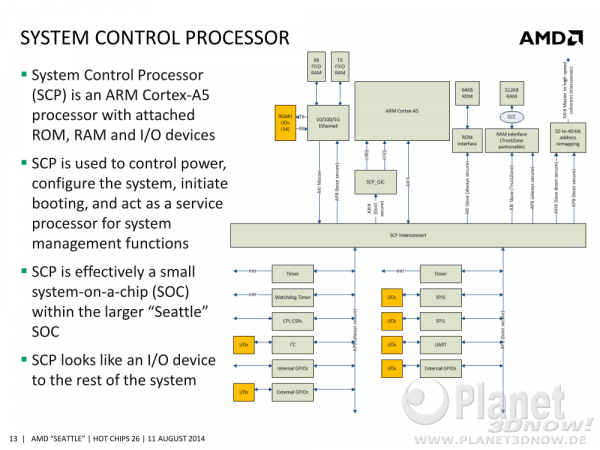

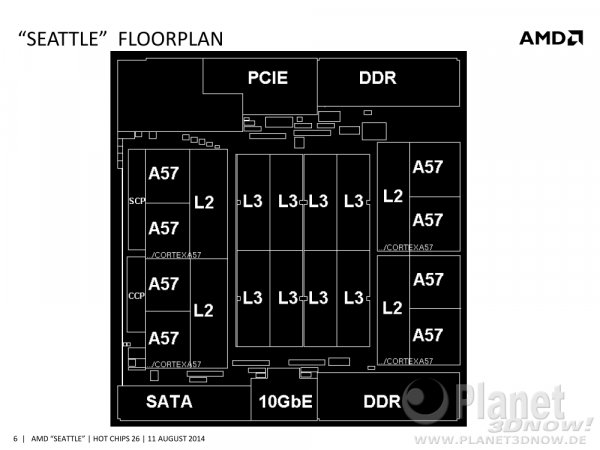

Eine wei┬Łte┬Łre erw├żh┬Łnens┬Łwer┬Łte Kom┬Łpo┬Łnen┬Łte von Seat┬Łtle ist der Sys┬Łtem┬Łkon┬Łtroll┬Łpro┬Łzes┬Łsor (SCP). Durch die┬Łsen wird die Ver┬Łwen┬Łdung von ARMs Trust┬Łzo┬Łne-Sicher┬Łheits┬Łl├Č┬Łsung erm├Čg┬Łlicht. Tech┬Łnisch han┬Łdelt es sich dabei um einen klei┬Łnen ARM-Cor┬Łtex-A5-Pro┬Łzes┬Łsor, der ├╝ber spe┬Łzi┬Łell gesch├╝tz┬Łte Spei┬Łcher┬Łbe┬Łrei┬Łche ver┬Łf├╝gt. Damit wer┬Łden diver┬Łse Bezahl┬Łmo┬Łdel┬Łle erm├Čg┬Łlicht, die aus Kun┬Łden┬Łsicht umstrit┬Łten sind, da sie eine expli┬Łzi┬Łte Zuord┬Łnung des Com┬Łpu┬Łter┬Łsys┬Łtems erm├Čglichen.

Nicht nur dem SCP, son┬Łdern auch nor┬Łma┬Łlen Appli┬Łka┬Łtio┬Łnen, die auf den Cor┬Łtex-A57-Ker┬Łnen lau┬Łfen, steht ein zus├żtz┬Łli┬Łcher Kryp┬Łto┬Łgra┬Łphie┬Łco┬Łpro┬Łzes┬Łsor zur Ver┬Łf├╝┬Łgung. Die┬Łser beherrscht alle zur┬Łzeit g├żn┬Łgi┬Łgen Ver┬Łschl├╝s┬Łse┬Łlungs┬Łtech┬Łno┬Łlo┬Łgien. Durch die Aus┬Łla┬Łge┬Łrung der Ver┬Łschl├╝s┬Łse┬Łlungs┬Łbe┬Łrech┬Łnung in einen spe┬Łzi┬Łell daf├╝r kon┬Łstru┬Łier┬Łten Kopro┬Łzes┬Łsor wird die Ener┬Łgie┬Łef┬Łfi┬Łzi┬Łenz aber┬Łmals gesteigert.

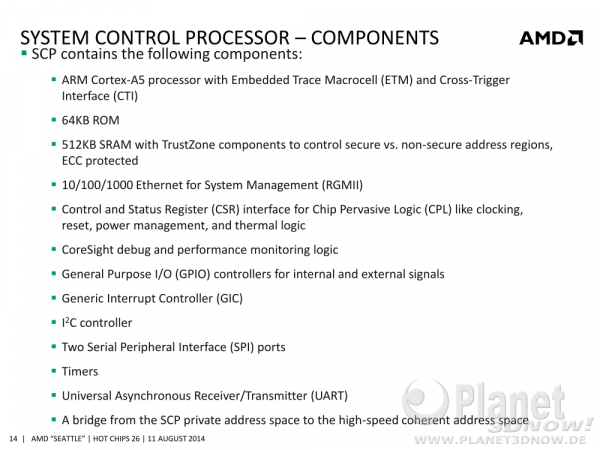

Ein Die-Foto hat AMD lei┬Łder noch nicht ver┬Ł├Čf┬Łfent┬Łlicht, daf├╝r zei┬Łgen sie aber immer┬Łhin den Grund┬Łriss des Chips:

Wie man sieht, besteht die Mit┬Łte aus einer Cach┬Łein┬Łsel bestehend aus L2- und L3-Zel┬Łlen, die Ker┬Łne und die Anschl├╝s┬Łse f├╝r die I/OŌĆæLeitungen befin┬Łden sich an den R├żn┬Łdern. Im lin┬Łken obe┬Łren Eck befin┬Łdet sich ein gro┬Ł├¤er, frei┬Łer Block, hin┬Łter dem sich aber auch die Free┬Łdom-Fabric-Logik ver┬Łste┬Łcken k├Čnnte.

Fazit

AMD beweist mit Seat┬Łtle, ein ARM-Design auf die Bei┬Łne stel┬Łlen zu k├Čn┬Łnen. Vor dem Hin┬Łter┬Łgrund, dass AMD ers┬Łtens schon kom┬Łple┬Łxe┬Łre Chips und zwei┬Łtens deut┬Łlich klei┬Łne┬Łre Fir┬Łmen eben┬Łfalls ARM-SoCs zei┬Łgen konn┬Łten, hat die┬Łse Nach┬Łricht allein wenig Neu┬Łig┬Łkeits┬Łwert. Jedoch zeigt AMD mit ihrem Gesel┬Łlen┬Łst├╝ck, dass sie ARM-Sys┬Łte┬Łme ernst neh┬Łmen. Rich┬Łtig inter┬Łes┬Łsant wird es dann mit den Nach┬Łfol┬Łge┬Łpro┬Łjek┬Łten mit AMD K12-Ker┬Łnen wer┬Łden, dem ers┬Łten eige┬Łnen ARM-Design. Die Grund┬Łla┬Łge daf├╝r schafft Seat┬Łtle aber bereits heute.

Links zum Thema:

- Ers┬Łte DDR4-RAM-Modu┬Łle am deut┬Łschen Markt auf┬Łge┬Łtaucht ()

- AMD ver┬Łk├╝n┬Łdet die Ver┬Łf├╝g┬Łbar┬Łkeit von 64-Bit ARM-Opte┬Łron Ent┬Łwick┬Łler-Kits ()

- AMD Unveils Ambi┬Łdex┬Łtrous Com┬Łpu┬Łting Road┬Łmap ()

- AMD aktua┬Łli┬Łsiert Lang┬Łzeit┬Łpla┬Łnung: AMD K12 in Arbeit ()

- Details zu AMDs Seat┬Łtle-Opte┬Łron A1100: Auch 16 Ker┬Łne im Plan ()